蝕刻技術(shù)在半導體封裝中一直是一個重要的制造工藝,但也存在一些新的發(fā)展和挑戰(zhàn),。

高分辨率和高選擇性:隨著半導體器件尺寸的不斷縮小,,對蝕刻工藝的要求也越來越高,。要實現(xiàn)更高的分辨率和選擇性,,需要開發(fā)更加精細的蝕刻劑和蝕刻工藝條件,以滿足小尺寸結(jié)構(gòu)的制備需求,。

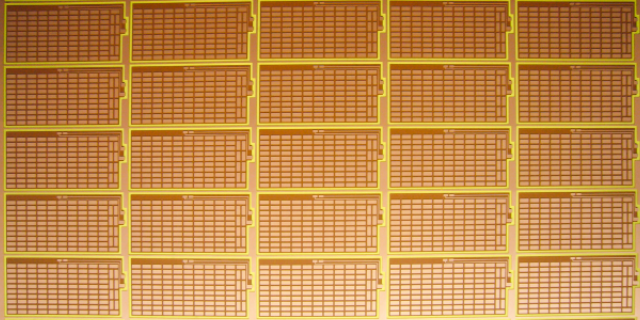

多層封裝:多層封裝是實現(xiàn)更高集成度和更小尺寸的關(guān)鍵,。然而,多層封裝也帶來了新的挑戰(zhàn),,如層間結(jié)構(gòu)的蝕刻控制,、深層結(jié)構(gòu)的蝕刻難度等。因此,,需要深入研究多層封裝中的蝕刻工藝,,并開發(fā)相應(yīng)的工藝技術(shù)來克服挑戰(zhàn)。

工藝控制和監(jiān)測:隨著蝕刻工藝的復(fù)雜性增加,,需要更精確的工藝控制和實時監(jiān)測手段,。開發(fā)先進的工藝控制和監(jiān)測技術(shù),如反饋控制系統(tǒng)和實時表征工具,,可以提高蝕刻工藝的穩(wěn)定性和可靠性,。

環(huán)境友好性:蝕刻工藝產(chǎn)生的廢液和廢氣對環(huán)境造成影響。因此,開發(fā)更環(huán)保的蝕刻劑和工藝條件,,以減少對環(huán)境的負面影響,,是當前的研究方向之一。

總的來說,,蝕刻技術(shù)在半導體封裝中面臨著高分辨率,、多層封裝、新材料和納米結(jié)構(gòu),、工藝控制和監(jiān)測以及環(huán)境友好性等方面的新發(fā)展和挑戰(zhàn)。解決這些挑戰(zhàn)需要深入研究和創(chuàng)新,,以推動蝕刻技術(shù)在半導體封裝中的進一步發(fā)展,。蝕刻技術(shù):半導體封裝中的材料選擇的關(guān)鍵!上海優(yōu)勢半導體封裝載體

利用蝕刻技術(shù)實現(xiàn)半導體封裝的先進方法有以下幾種:

1. 塑料光阻蝕刻:將光阻涂覆在半導體器件表面,,利用紫外線曝光將光阻區(qū)域暴露,,通過化學溶液將光刻圖案外的光阻溶解,暴露出需要刻蝕的區(qū)域,,然后使用化學蝕刻液對半導體器件進行刻蝕,。

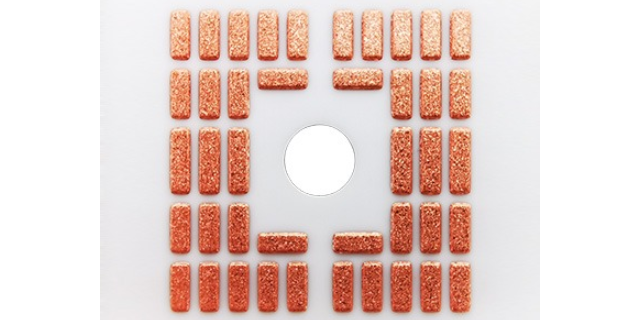

2. 基板蝕刻:將待封裝的半導體芯片放置在特定的化學溶液中,通過化學反應(yīng)溶解掉芯片上不需要的區(qū)域,。這種腐蝕方法常用于制作開窗孔或切口,。

3. 金屬蝕刻:在半導體封裝過程中,需要用到金屬材料(如銅,、鋁等)制作封裝元件,。利用化學蝕刻技術(shù),將金屬表面暴露在刻蝕液中,,刻蝕液會將不需要的金屬材料迅速溶解掉,,從而形成所需的金屬結(jié)構(gòu)。

4. 導電蝕刻:將具有電導性的液體浸泡在待蝕刻的區(qū)域,,利用電流通過蝕刻液與半導體器件之間建立電化學反應(yīng),,使得不需要的材料通過陽極溶解,從而實現(xiàn)精確的蝕刻,。這些是利用化學蝕刻技術(shù)實現(xiàn)半導體封裝的一些先進方法,,根據(jù)具體的封裝需求和材料特性,可以選擇適合的方法來實現(xiàn)半導體封裝過程中所需的蝕刻作業(yè),。上海優(yōu)勢半導體封裝載體蝕刻技術(shù)對于半導體封裝中電路導通的幫助,!

蝕刻工藝與半導體封裝器件功能集成是一個重要的研究領(lǐng)域,旨在將蝕刻工藝與封裝器件的功能需求相結(jié)合,,實現(xiàn)性能優(yōu)化和功能集成,。

1. 通道形狀控制:蝕刻工藝可以控制封裝器件的通道形狀,例如通過調(diào)制蝕刻劑的配方和蝕刻條件來實現(xiàn)微米尺寸的通道形狀調(diào)控。這種蝕刻調(diào)控可以實現(xiàn)更高的流體控制和熱傳輸效率,,優(yōu)化封裝器件的性能,。

2. 孔隙控制:蝕刻工藝可以通過控制蝕刻劑的濃度、溫度和蝕刻時間等參數(shù),,實現(xiàn)對封裝器件中孔隙形狀和大小的控制,。合理的孔隙設(shè)計可以提高封裝器件的介電性能、熱傳導性和穩(wěn)定性,。

3,。 電極形貌調(diào)控:蝕刻工藝可以用于調(diào)控封裝器件中電極的形貌和結(jié)構(gòu),例如通過選擇合適的蝕刻劑和蝕刻條件來實現(xiàn)電極的納米級精細加工,。這種電極形貌調(diào)控可以改善電極的界面特性和電流傳輸效率,,提高封裝器件的性能。

4. 保護層和阻隔層制備:蝕刻工藝可以用于制備封裝器件中的保護層和阻隔層,,提高器件的封裝性能和可靠性,。通過選擇合適的蝕刻劑和工藝條件,可以實現(xiàn)保護層和阻隔層的高質(zhì)量制備,,并確保其與器件的良好兼容性,。

總之,蝕刻工藝與半導體封裝器件功能集成的研究旨在通過精確控制蝕刻工藝參數(shù),,實現(xiàn)對封裝器件結(jié)構(gòu),、形貌和性能的有效調(diào)控,以滿足不同應(yīng)用需求,。

在半導體封裝過程中,,蝕刻和材料選擇對封裝阻抗控制有著重要的影響。蝕刻過程可以調(diào)整封裝材料的形狀和幾何結(jié)構(gòu),,從而改變器件的尺寸和電性能,。材料選擇則決定了封裝材料的電學特性,包括介電常數(shù)和導電性等,。

蝕刻對阻抗的影響主要通過改變電磁場和電流的分布來實現(xiàn),。通過控制蝕刻參數(shù),如蝕刻深度,、蝕刻速率和蝕刻劑的組成,,可以調(diào)整封裝材料的幾何形狀和厚度,從而影響器件的阻抗特性,。例如,,通過蝕刻可以實現(xiàn)更窄的線寬和間距,從而降低線路的阻抗,。

材料選擇對阻抗的影響主要體現(xiàn)在材料的介電常數(shù)和導電性上,。不同的封裝材料具有不同的介電常數(shù),介電常數(shù)的不同會導致信號的傳播速度和阻抗發(fā)生變化。此外,,選擇具有適當導電性的封裝材料可以提供更低的電阻和更好的信號傳輸性能,。

因此,研究蝕刻和材料選擇對半導體封裝阻抗控制的關(guān)系可以幫助優(yōu)化封裝過程,,提高封裝器件的性能和可靠性,。這對于半導體行業(yè)來說是非常重要的,可以為開發(fā)和制造高性能的半導體器件提供技術(shù)支持,。半導體封裝技術(shù)的分類和特點,。

環(huán)境友好型半導體封裝載體的開發(fā)與應(yīng)用研究是指在半導體封裝領(lǐng)域,針對環(huán)境保護和可持續(xù)發(fā)展的要求,,研發(fā)和應(yīng)用具有環(huán)境友好性能的封裝載體材料和技術(shù),。

材料選擇與設(shè)計:選擇環(huán)境友好的材料,如可降解高分子材料,、無鹵素阻燃材料等,,以減少對環(huán)境的影響,。設(shè)計和優(yōu)化材料組合和結(jié)構(gòu),,以滿足封裝載體的性能和可靠性要求。

節(jié)能降耗技術(shù):在封裝載體的制造過程中,,采用節(jié)能降耗的技術(shù),,如低溫封裝技術(shù)、節(jié)能設(shè)備等,,以減少資源消耗和對環(huán)境的負面影響,。

廢棄物管理和循環(huán)利用:研究和推廣有效的廢棄物管理和循環(huán)利用技術(shù),將封裝載體的廢棄物進行分類,、回收和再利用,,減少對環(huán)境的污染和資源的浪費。

綠色封裝工藝和工具:推進綠色封裝工藝和工具的研發(fā)和應(yīng)用,,如環(huán)境友好型封裝膠水,、無鹵素阻燃劑等,在減少環(huán)境污染的同時,,提高封裝工藝的效率和質(zhì)量,。

環(huán)境評估和認證:對環(huán)境友好型半導體封裝載體進行環(huán)境評估和認證,確保其符合相關(guān)環(huán)保法規(guī)和標準,,為企業(yè)及產(chǎn)品在市場上競爭提供優(yōu)勢,。

需要綜合考慮材料選擇、節(jié)能降耗技術(shù),、廢棄物管理和循環(huán)利用,、綠色封裝工藝和工具等方面,推動環(huán)保意識的傳播和技術(shù)的創(chuàng)新,促進半導體封裝行業(yè)向環(huán)境友好型方向發(fā)展,。蝕刻技術(shù)如何實現(xiàn)半導體封裝中的電路互聯(lián),!上海優(yōu)勢半導體封裝載體

半導體封裝技術(shù)中的熱管理和電力傳輸。上海優(yōu)勢半導體封裝載體

蝕刻與電子封裝界面的界面相容性研究主要涉及的是如何在蝕刻過程中保護電子封裝結(jié)構(gòu),,防止蝕刻劑侵入導致材料損傷或結(jié)構(gòu)失效的問題,。

首先,需要考慮蝕刻劑的選擇,,以確保其與電子封裝材料之間的相容性,。不同的材料對不同的蝕刻劑具有不同的抵抗能力,因此需要選擇適合的蝕刻劑,,以避免對電子封裝結(jié)構(gòu)造成損害,。

其次,需要設(shè)計合適的蝕刻工藝參數(shù),,以保護電子封裝結(jié)構(gòu),。這包括確定蝕刻劑的濃度、蝕刻時間和溫度等參數(shù),,以確保蝕刻劑能夠在一定程度上去除目標材料,,同時盡量減少對電子封裝結(jié)構(gòu)的影響。

此外,,還可以通過添加保護層或采用輔助保護措施來提高界面相容性,。例如,可以在電子封裝結(jié)構(gòu)表面涂覆一層保護膜,,以減少蝕刻劑對結(jié)構(gòu)的侵蝕,。

在研究界面相容性時,還需要進行一系列的實驗和測試,,以評估蝕刻過程對電子封裝結(jié)構(gòu)的影響,。這包括材料性能測試、顯微鏡觀察,、電性能測試等,。通過實驗數(shù)據(jù)的分析和對結(jié)果的解釋,可以進一步優(yōu)化蝕刻工藝參數(shù),,以提高界面相容性,。

總的來說,蝕刻與電子封裝界面的界面相容性研究是一個復(fù)雜而細致的工作,,需要綜合考慮材料性質(zhì),、蝕刻劑選擇、工藝參數(shù)控制等多個因素,,以確保蝕刻過程中對電子封裝結(jié)構(gòu)的保護和保持其功能穩(wěn)定性,。上海優(yōu)勢半導體封裝載體